Hi,

I’m currently viewing Linux running on the A10 SoC HPS through the serial terminal. My issue is that everytime I program my FPGA, the serial terminal freezes. Is this because I need to modify U-Boot, the device tree blob file, etc. or is the serial terminal supposed to freeze and I am not correctly viewing the HPS ? Essentially, I want to execute a program on the HPS after I program the FPGA.

Thank you,

Hello,

there are planty possibilities how terminal could freeze. Could You describe Your problem in a more detaile, please? E.g. Are You using Golden Reference Hardware/Software Designes. And how did You get it (from source, compile with YoctoProject, …)? How are You programing FPGA?

The problem is that the HPS gets reset when you load the FPGA. In Cyclone V SoC boards I always use MSEL = 00000, load from SD card. And then i load the FPGA from Quartus and the HPS keeps running. Try that instead of putting MSEL in the recommended mode for laoding FPGA from USB Blaster.

Regards

Hello again,

just for information:

I use Cyclone V but I have not got any problem with serial link during FPGA reconfiguration - nor from programming via U-Boot, nor from programming via Linux, nor for progrmming with Quartus Programmer or Quartus Signal Tap II via JTAG. And I use recommended MSEL configuration.

I am currently using the GSRD files. I am however trying to program custom hardware files (not GHRD). I have not gone through the process of compiling via YoctoProject as of yet. Would it be correct to say if I go through the GSRD flow process (described https://rocketboards.org/foswiki/Documentation/AVCVGSRD171) then the serial terminal would not freeze ?

As a follow up question, are there other ways to view the HPS system if not through the serial terminal ?

Hello,

well, if You are trying to program FPGA with Your own design, it may need its own DeviceTree file. It is need in case You add, remove or change some parts of design in comparation with GRSD such as e.g. peripherals of HPS IP core in QSys.

The other possible source of problem would be incorrect FPGA design. The serial link to processor has to be set in Qsys in HPS IP core in a very same way as in GRHD. The proper settings would differ according to Your board, however, so try to look at the page of Your board at RocketBoards. There You will find the right GRHD and the proper settings.

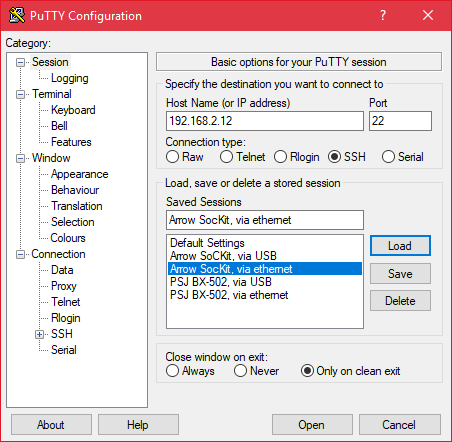

And to answer Yours second question - You can open session beside serial link also via ethernet. SSH protocol is used for this way. If You use PuTTY, You only need to switch ‘serial’ to ‘SSH’ and type IP address of Your board.

However, You will not be able to connect as ‘root’ user (with password verification), due to default security settings. If You would like to try it, You could find details here: https://forum.rocketboards.org/t/transfer-file-on-sd-card-from-windows-host/1520/5?u=jankonecny.

Best wishes.

Jan Konečný.

Why dont you modify the GHRD?? Maybe you are badly configuring the HPS in the Qsys instantiation.

I suposse you have the HPS instantiated but if you dont the HPS wont work to save power.

Jan,

Thanks for the input. I had a feeling that I would have to make a new Device Tree file. I will also look into the serial link IP instantiation in Qsys - I did not know about that. Thank you.

MP

I was in the process of working backwards from the GHRD but was having difficulty understanding some of the setup in Qsys. I will try again to pare down the GHRD and see if I am able to properly compile. Will keep forum updated.

Thank you,

MP

Unlike Cyclone V Arria 10 devices cannot load the FPGA without rebooting the HPS unless you use the device tree overlay strategy. In Cyclone V the HPS and FPGA can be considered as separate entities. In Arria 10 the FPGA must be configured for the HPS to have access to the DDR memory. When you’re re-programming the FPGA your essentially taking the DDR memory interface down and that’s why your terminal is freezing (Linux will lockup). With Arria 10 the easiest way to get started booting your own FPGA code is to start with the GHRD. Make sure you know how to generate the preloader and device tree and boot it using files you’ve created yourself (re-compiled RBF’s, preloader, and dtb). After that add/remove what you want to the FPGA firmware. Depending on what you’ve changed you might need to re-generate the preloader (uboot) and device tree. You could try replacing the GHRD RBF’s on the SD card (or however your booting) with yours first and see if it boots.

Assuming an SD card and that you’ve copied the preloader to the card using scp (etc) while the board is running:

The RBF’s and DTB are files you can easily replace on the FAT partition.

I do not remember what partition is the raw (type 0xA2) on the SD card for the GHRD. Assuming it’s partition 3 (/dev/mmcblk0p3) on the card here’s how you can update the preloader: You can run fdisk -l in the terminal to determine which partition is type 0xA2 (raw) if you’re not sure.

writing:

dd if=uboot_w_dtb-mkpimage.bin of=/dev/mmcblk0p3 bs=64k seek=0

reading: (1,048,576 bytes - size of uboot_w_dtb-mkpimage.bin)

dd if=/dev/mmcblk0p3 of=/tmp/raw.bin bs=64k seek=0 count=16

If the SD card is in a Linux PC then /dev/mmcblk0p3 might look more like /dev/sdc3 (assuming sdc). Once again use fdisk -l or use df if the was auto mounted.

Hope this helps. Cheers!