if I follow source 1, then I managed to start the system. the system displays the following messages after startup:

U-Boot SPL 2013.01.01 (Jan 23 2018 - 19:49:55)

BOARD : Altera SOCFPGA Cyclone V Board

CLOCK: EOSC1 clock 25000 KHz

CLOCK: EOSC2 clock 25000 KHz

CLOCK: F2S_SDR_REF clock 0 KHz

CLOCK: F2S_PER_REF clock 0 KHz

CLOCK: MPU clock 800 MHz

CLOCK: DDR clock 400 MHz

CLOCK: UART clock 100000 KHz

CLOCK: MMC clock 50000 KHz

CLOCK: QSPI clock 3125 KHz

RESET: COLD

INFO : Watchdog enabled

SDRAM: Initializing MMR registers

SDRAM: Calibrating PHY

SEQ.C: Preparing to start memory calibration

SEQ.C: CALIBRATION PASSED

SDRAM: 1024 MiB

ALTERA DWMMC: 0

reading u-boot.img

reading u-boot.img

U-Boot 2013.01.01-00138-g239ae4d (Jan 23 2018 - 20:01:02)

CPU : Altera SOCFPGA Platform

BOARD : Altera SOCFPGA Cyclone V Board

I2C: ready

DRAM: 1 GiB

MMC: ALTERA DWMMC: 0

*** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

Skipped ethaddr assignment due to invalid EMAC address in EEPROM

Net: mii0

Warning: failed to set MAC address

Hit any key to stop autoboot: 0

reading u-boot.scr

589 bytes read in 5 ms (114.3 KiB/s)

Executing script at 02000000

– Programming FPGA –

reading soc_system.rbf

2199000 bytes read in 125 ms (16.8 MiB/s)

Starting application at 0x3FF7957C …

Application terminated, rc = 0x0

– Setting Env Variables –

reading zImage

4437200 bytes read in 281 ms (15.1 MiB/s)

reading soc_system.dtb

24470 bytes read in 7 ms (3.3 MiB/s)

Flattened Device Tree blob at 00000100

Booting using the fdt blob at 0x00000100

Loading Device Tree to 03ff7000, end 03ffff95 … OK

Starting kernel …

[ 0.000000] Booting Linux on physical CPU 0x0

[ 0.000000] Linux version 4.11.0 (vlasovdv0111@vlasovdv0111-X555LJ) (gcc ver8

[ 0.000000] CPU: ARMv7 Processor [413fc090] revision 0 (ARMv7), cr=10c5387d

[ 0.000000] CPU: PIPT / VIPT nonaliasing data cache, VIPT aliasing instructie

[ 0.000000] OF: fdt: Machine model: Terasic DE10 NANO

[ 0.000000] Memory policy: Data cache writealloc

[ 0.000000] percpu: Embedded 16 pages/cpu @ef7c5000 s35212 r8192 d22132 u6556

[ 0.000000] Built 1 zonelists in Zone order, mobility grouping on. Total pa8

[ 0.000000] Kernel command line: console=ttyS0,115200 root=/dev/mmcblk0p2 rwt

[ 0.000000] PID hash table entries: 4096 (order: 2, 16384 bytes)

[ 0.000000] Dentry cache hash table entries: 131072 (order: 7, 524288 bytes)

[ 0.000000] Inode-cache hash table entries: 65536 (order: 6, 262144 bytes)

[ 0.000000] Memory: 1028432K/1048576K available (7168K kernel code, 479K rwd)

[ 0.000000] Virtual kernel memory layout:

[ 0.000000] vector : 0xffff0000 - 0xffff1000 ( 4 kB)

[ 0.000000] fixmap : 0xffc00000 - 0xfff00000 (3072 kB)

[ 0.000000] vmalloc : 0xf0800000 - 0xff800000 ( 240 MB)

[ 0.000000] lowmem : 0xc0000000 - 0xf0000000 ( 768 MB)

[ 0.000000] pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

[ 0.000000] modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

[ 0.000000] .text : 0xc0008000 - 0xc0800000 (8160 kB)

[ 0.000000] .init : 0xc0a00000 - 0xc0b00000 (1024 kB)

[ 0.000000] .data : 0xc0b00000 - 0xc0b77fc8 ( 480 kB)

[ 0.000000] .bss : 0xc0b77fc8 - 0xc0ba12c4 ( 165 kB)

[ 0.000000] SLUB: HWalign=64, Order=0-3, MinObjects=0, CPUs=2, Nodes=1

[ 0.000000] Hierarchical RCU implementation.

[ 0.000000] RCU debugfs-based tracing is enabled.

[ 0.000000] Build-time adjustment of leaf fanout to 32.

[ 0.000000] NR_IRQS:16 nr_irqs:16 16

[ 0.000000] L2C-310 erratum 769419 enabled

[ 0.000000] L2C-310 enabling early BRESP for Cortex-A9

[ 0.000000] L2C-310 full line of zeros enabled for Cortex-A9

[ 0.000000] L2C-310 dynamic clock gating enabled, standby mode enabled

[ 0.000000] L2C-310 cache controller enabled, 8 ways, 512 kB

[ 0.000000] L2C-310: CACHE_ID 0x410030c9, AUX_CTRL 0x46060001

[ 0.000000] clocksource: timer: mask: 0xffffffff max_cycles: 0xffffffff, maxs

[ 0.000006] sched_clock: 32 bits at 100MHz, resolution 10ns, wraps every 214s

[ 0.000019] Switching to timer-based delay loop, resolution 10ns

[ 0.000254] GIC: PPI13 is secure or misconfigured

[ 0.000293] GIC: PPI13 is secure or misconfigured

[ 0.000480] Console: colour dummy device 80x30

[ 0.000506] Calibrating delay loop (skipped), value calculated using timer f)

[ 0.000523] pid_max: default: 32768 minimum: 301

[ 0.000638] Mount-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.000651] Mountpoint-cache hash table entries: 2048 (order: 1, 8192 bytes)

[ 0.001183] CPU: Testing write buffer coherency: ok

[ 0.001214] ftrace: allocating 23293 entries in 69 pages

[ 0.042037] CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

[ 0.042546] Setting up static identity map for 0x100000 - 0x100058

[ 0.043153] smp: Bringing up secondary CPUs …

[ 0.043747] GIC: PPI13 is secure or misconfigured

[ 0.043759] CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

[ 0.043842] smp: Brought up 1 node, 2 CPUs

[ 0.043859] SMP: Total of 2 processors activated (400.00 BogoMIPS).

[ 0.043866] CPU: All CPU(s) started in SVC mode.

[ 0.044736] devtmpfs: initialized

[ 0.049567] VFP support v0.3: implementor 41 architecture 3 part 30 variant 4

[ 0.049783] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, ms

[ 0.049803] futex hash table entries: 512 (order: 3, 32768 bytes)

[ 0.050722] NET: Registered protocol family 16

[ 0.051527] DMA: preallocated 256 KiB pool for atomic coherent allocations

[ 0.053227] hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint.

[ 0.053240] hw-breakpoint: maximum watchpoint size is 4 bytes.

[ 0.075429] vgaarb: loaded

[ 0.075705] SCSI subsystem initialized

[ 0.075938] usbcore: registered new interface driver usbfs

[ 0.075995] usbcore: registered new interface driver hub

[ 0.076054] usbcore: registered new device driver usb

[ 0.076203] usb_phy_generic sopc@0:usbphy@0: sopc@0:usbphy@0 supply vcc not r

[ 0.077085] pps_core: LinuxPPS API ver. 1 registered

[ 0.077095] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giom>

[ 0.077119] PTP clock support registered

[ 0.077284] FPGA manager framework

[ 0.079292] clocksource: Switched to clocksource timer

[ 0.131364] NET: Registered protocol family 2

[ 0.131884] TCP established hash table entries: 8192 (order: 3, 32768 bytes)

[ 0.131964] TCP bind hash table entries: 8192 (order: 4, 65536 bytes)

[ 0.132091] TCP: Hash tables configured (established 8192 bind 8192)

[ 0.132194] UDP hash table entries: 512 (order: 2, 16384 bytes)

[ 0.132242] UDP-Lite hash table entries: 512 (order: 2, 16384 bytes)

[ 0.132401] NET: Registered protocol family 1

[ 0.132793] RPC: Registered named UNIX socket transport module.

[ 0.132804] RPC: Registered udp transport module.

[ 0.132811] RPC: Registered tcp transport module.

[ 0.132818] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.133479] hw perfevents: enabled with armv7_cortex_a9 PMU driver, 7 countee

[ 0.135317] workingset: timestamp_bits=30 max_order=18 bucket_order=0

[ 0.144661] NFS: Registering the id_resolver key type

[ 0.144691] Key type id_resolver registered

[ 0.144699] Key type id_legacy registered

[ 0.144716] Installing knfsd (copyright (C) 1996 okir@monad.swb.de).

[ 0.145377] ntfs: driver 2.1.32 [Flags: R/W].

[ 0.145661] jffs2: version 2.2. (NAND) �© 2001-2006 Red Hat, Inc.

[ 0.146983] bounce: pool size: 64 pages

[ 0.146997] io scheduler noop registered (default)

[ 0.147005] io scheduler mq-deadline registered

[ 0.155228] dma-pl330 ffe01000.dma: Loaded driver for PL330 DMAC-341330

[ 0.155247] dma-pl330 ffe01000.dma: DBUFF-512x8bytes Num_Chans-8 Num_Peri-38

[ 0.160162] Serial: 8250/16550 driver, 2 ports, IRQ sharing disabled

[ 0.161333] console [ttyS0] disabled

[ 0.161371] ffc02000.serial: ttyS0 at MMIO 0xffc02000 (irq = 24, base_baud =A

[ 0.760992] console [ttyS0] enabled

[ 0.766223] brd: module loaded

[ 0.771229] libphy: Fixed MDIO Bus: probed

[ 0.776189] CAN device driver interface

[ 0.780468] socfpga-dwmac ff702000.ethernet: snps,phy-addr property is depred

[ 0.788005] socfpga-dwmac ff702000.ethernet: PTP uses main clock

[ 0.794106] stmmac - user ID: 0x10, Synopsys ID: 0x37

[ 0.799141] socfpga-dwmac ff702000.ethernet: Ring mode enabled

[ 0.804969] socfpga-dwmac ff702000.ethernet: DMA HW capability register suppd

[ 0.812433] socfpga-dwmac ff702000.ethernet: Enhanced/Alternate descriptors

[ 0.819377] socfpga-dwmac ff702000.ethernet: Enabled extended descriptors

[ 0.826137] socfpga-dwmac ff702000.ethernet: RX Checksum Offload Engine suppd

[ 0.833599] socfpga-dwmac ff702000.ethernet: COE Type 2

[ 0.838803] socfpga-dwmac ff702000.ethernet: TX Checksum insertion supported

[ 0.845834] socfpga-dwmac ff702000.ethernet: Enable RX Mitigation via HW Watr

[ 0.861227] libphy: stmmac: probed

[ 0.864629] socfpga-dwmac ff702000.ethernet (unnamed net_device) (uninitialie

[ 0.877678] dwc2 ffb40000.usb: ffb40000.usb supply vusb_d not found, using dr

[ 0.885987] dwc2 ffb40000.usb: ffb40000.usb supply vusb_a not found, using dr

[ 0.894390] dwc2 ffb40000.usb: EPs: 16, dedicated fifos, 8064 entries in SPRM

[ 0.901968] dwc2 ffb40000.usb: DWC OTG Controller

[ 0.906680] dwc2 ffb40000.usb: new USB bus registered, assigned bus number 1

[ 0.913741] dwc2 ffb40000.usb: irq 36, io mem 0xffb40000

[ 0.919824] hub 1-0:1.0: USB hub found

[ 0.923595] hub 1-0:1.0: 1 port detected

[ 0.928248] usbcore: registered new interface driver usb-storage

[ 0.934560] i2c /dev entries driver

[ 0.939354] Synopsys Designware Multimedia Card Interface Driver

[ 0.945643] dw_mmc ff704000.flash: IDMAC supports 32-bit address mode.

[ 0.952203] dw_mmc ff704000.flash: Using internal DMA controller.

[ 0.958277] dw_mmc ff704000.flash: Version ID is 240a

[ 0.963362] dw_mmc ff704000.flash: DW MMC controller at irq 35,32 bit host do

[ 0.972626] dw_mmc ff704000.flash: Got CD GPIO

[ 0.977095] mmc_host mmc0: card is polling.

[ 1.009251] mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 400000H)

[ 1.039284] dw_mmc ff704000.flash: 1 slots initialized

[ 1.045517] ledtrig-cpu: registered to indicate activity on CPUs

[ 1.051719] usbcore: registered new interface driver usbhid

[ 1.057268] usbhid: USB HID core driver

[ 1.061356] fpga_manager fpga0: Altera SOCFPGA FPGA Manager registered

[ 1.068441] altera_hps2fpga_bridge sopc@0:fpgabridge@0: fpga bridge [hps2fpgd

[ 1.076835] altera_hps2fpga_bridge sopc@0:fpgabridge@1: fpga bridge [lwhps2fd

[ 1.085306] altera_hps2fpga_bridge sopc@0:fpgabridge@2: fpga bridge [fpga2hpd

[ 1.093829] altera_fpga2sdram_bridge sopc@0:fpgabridge@3: fpga bridge [fpga2d

[ 1.102340] altera_fpga2sdram_bridge sopc@0:fpgabridge@3: driver initializedf

[ 1.111616] oprofile: using arm/armv7-ca9

[ 1.116371] NET: Registered protocol family 10

[ 1.121565] Segment Routing with IPv6

[ 1.125287] sit: IPv6, IPv4 and MPLS over IPv4 tunneling driver

[ 1.131844] NET: Registered protocol family 17

[ 1.136288] NET: Registered protocol family 15

[ 1.140753] can: controller area network core (rev 20120528 abi 9)

[ 1.146954] NET: Registered protocol family 29

[ 1.151402] can: raw protocol (rev 20120528)

[ 1.155656] can: broadcast manager protocol (rev 20161123 t)

[ 1.161310] can: netlink gateway (rev 20130117) max_hops=1

[ 1.166973] 8021q: 802.1Q VLAN Support v1.8

[ 1.171196] Key type dns_resolver registered

[ 1.175522] ThumbEE CPU extension supported.

[ 1.179802] Registering SWP/SWPB emulation handler

[ 1.187343] hctosys: unable to open rtc device (rtc0)

[ 1.192409] of_cfs_init

[ 1.194911] of_cfs_init: OK

[ 1.198226] ttyS0 - failed to request DMA

[ 1.202619] Waiting for root device /dev/mmcblk0p2…

[ 1.259727] mmc_host mmc0: Bus speed (slot 0) = 50000000Hz (slot req 5000000)

[ 1.269516] mmc0: new high speed SDHC card at address 0001

[ 1.275416] mmcblk0: mmc0:0001 00000 7.44 GiB

[ 1.280923] mmcblk0: p1 p2 p3

[ 1.289955] EXT4-fs (mmcblk0p2): couldn’t mount as ext3 due to feature incoms

[ 1.316304] random: fast init done

[ 1.332743] EXT4-fs (mmcblk0p2): recovery complete

[ 1.343578] EXT4-fs (mmcblk0p2): mounted filesystem with ordered data mode. )

[ 1.351690] VFS: Mounted root (ext4 filesystem) on device 179:2.

[ 1.359371] devtmpfs: mounted

[ 1.363292] Freeing unused kernel memory: 1024K

[ 1.486388] EXT4-fs (mmcblk0p2): re-mounted. Opts: data=ordered

Starting logging: OK

Initializing random number generator… done.

Starting network: OK

Welcome!

Vlasovdv0111 login: [ 127.149286] random: crng init done

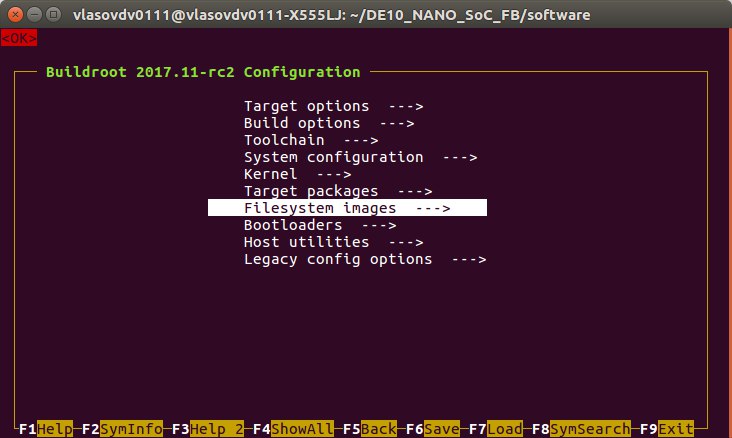

At the same time, it is impossible to enter any messages into the terminal. In this connection, I do not know why the system does not work with the new pbf file. And also there is a difficulty with Step Step 7.1 – Configuring Buildroot. Namely, trying to save the configuration the program seems to hang and from it you can not go out except if you close the terminal.