Hi all can anyone tell me how can I see transceiver output (received parallel data) on my putty terminal. I have already tried connecting transceiver to HPS and trying to access transceiver base address to see output but that doesnt work? Any suggestions please…

Transceivers are a very large topic. I guess my first question is, what protocol are you running and what IP do you have connected up to the transceiver?

If you have no IP connected to the transceiver, exactly what is your set-up?

@SusananhM

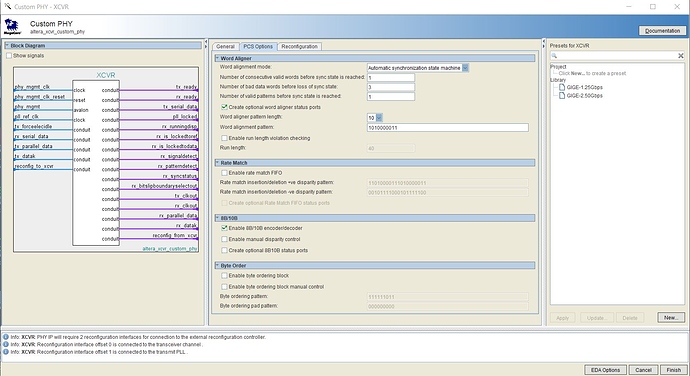

Hi, thank you so much for your reply. So, Here is my setup. I have simply a register connected to Avalon interface. The received data from a transceiver is connected to this register and is read via Avalon interface. I hope that it works. I am running my transceiver on GIGE protocol. In figure you can find the transceiver configuration for altera.

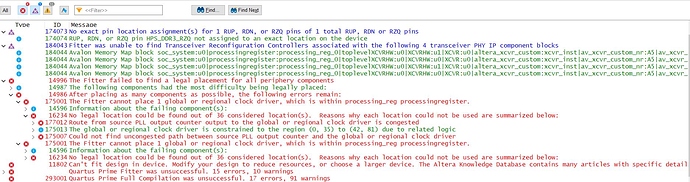

Now whenever I synthesize my design, I get no error but whenever I compile my design, I get this error

14996: The fitter failed to find a legal replacement for all the peripheral components.

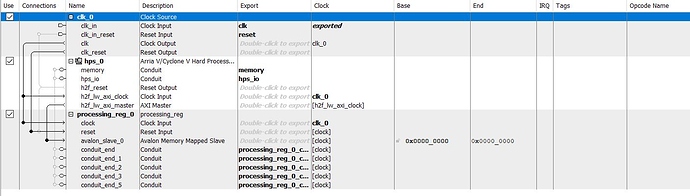

Any ideas what I am doing wrong. Here is my soc_system

I have also attached my verilog files here with. Can you please tell me what i can do to remove this error?

//Processing Register which is connected to Avalon interface.

// I want to get output of this register at putty hence in other words transceiver output at my putty terminal

module processingregister(

input clk,

input reset,

input write,

input [7:0] writedata,

input read,

output [7:0] readdata,

input RX_SERIAL_DATA,

input RX_SERIAL_DATA1,

output TX_SERIAL_DATA,

output TX_SERIAL_DATA1,

output [7:0] RX_PARALLEL_DATA1

//output RX_SYNC_STATUS1

);

reg [7:0] Regreaddata;

//call pll module here and connect it to this wire

wire CLK65M;

assign readdata=Regreaddata;

toplevelXCVRHW u0(

.CLK(clk),

.RST(reset),

.RX_serial_data(RX_SERIAL_DATA),

.RX_serial_data1(RX_SERIAL_DATA1),

.TX_serial_data(TX_SERIAL_DATA),

.TX_serial_data1(TX_SERIAL_DATA1),

.RX_parallel_data1(RX_PARALLEL_DATA1)

//.RX_SYNC_STATUS1(RX_SYNC_STATUS1)

// .CLK65M(CLK65M)

);

pll u1(

.refclk(clk), // refclk.clk

.rst(reset), // reset.reset

.outclk_0(CLK65M) // outclk0.clk

);

//logic that synchronizes the register with the transceiver output//

//I have to sync register to the pll ref clock of the transceiver so that

//at pll data goes to the register

// then at write or read data needs to go to the output

always @ (posedge CLK65M)

begin

if(reset)

begin

Regreaddata<=0;

end

//else if(write | RX_SYNC_STATUS1 | read)

else

begin

Regreaddata<=RX_PARALLEL_DATA1;

end

end

endmodule

//transceiver that is connected to receiver

module toplevelXCVRHW(

input CLK,

input RST,

input RX_serial_data,

input RX_serial_data1,

output TX_serial_data,

output TX_serial_data1,

output [7:0] RX_parallel_data,

output [7:0] RX_parallel_data1

//output RX_SYNC_STATUS,

//output RX_SYNC_STATUS1

//output CLK65M

);

XCVRHW u0(

.CLK50(CLK),

.RESET(RST),

.TX_serial_data(TX_serial_data),

.RX_serial_data(RX_serial_data),

.RX_parallel_data(RX_parallel_data)

//.RX_SYNCSTATUS(RX_SYNC_STATUS)

//.CLK65M(CLK65M)

);

XCVRHW u1(

.CLK50(CLK),

.RESET(RST),

.TX_serial_data(TX_serial_data1),

.RX_serial_data(RX_serial_data1),

.RX_parallel_data(RX_parallel_data1)

//.RX_SYNCSTATUS(RX_SYNC_STATUS1)

);

endmodule

//xcvr module

module XCVRHW

(

input CLK50,

input RESET,

output TX_serial_data,

input RX_serial_data,

output [7:0] RX_parallel_data,

//////////////////////////////////////////

/////////////////////////////////////////

//output TX_ready,

//output RX_ready,

//output RX_runningdisp,

//output RX_patterndetect,

output RX_SYNCSTATUS

//output CLK65M

//output TX_clkout,

//output RX_clkout,

//output RX_datak,

//output clk5k,

//output clk1hz,

//output [7:0]TX_PAR_DATA,

//output clk5Mhz

);

wire CLK65MHz;

wire RX_syncstatus;

wire [7:0] CCHAR;

wire [7:0] COUNTCHAR;

wire [7:0] TX_parallel_data;

assign RX_SYNCSTATUS=RX_syncstatus;

//assign CLK65M = CLK65MHz;

XCVR u0(

.phy_mgmt_clk(CLK50),

.phy_mgmt_clk_reset(RESET), // phy_mgmt_clk_reset.reset

/*

.phy_mgmt_address(), // phy_mgmt.address

.phy_mgmt_read(), // .read

.phy_mgmt_readdata(), // .readdata

.phy_mgmt_waitrequest(), // .waitrequest

.phy_mgmt_write(), // .write

.phy_mgmt_writedata(), // .writedata

*/

// .tx_ready(TX_ready), // tx_ready.export

// .rx_ready(RX_ready), // rx_ready.export

.pll_ref_clk(CLK65MHz),

//.pll_ref_clk(CLK65MHz), // pll_ref_clk.clk

.tx_serial_data(TX_serial_data), // tx_serial_data.export

//.pll_locked(), // pll_locked.export

.rx_serial_data(RX_serial_data), // rx_serial_data.export

//.rx_runningdisp(RX_runningdisp), // rx_runningdisp.export

//.rx_patterndetect(RX_patterndetect), // rx_patterndetect.export

.rx_syncstatus(RX_syncstatus), // rx_syncstatus.export

// output wire [4:0] rx_bitslipboundaryselectout, // rx_bitslipboundaryselectout.export

//.tx_clkout(TX_clkout), // tx_clkout.export

//.rx_clkout(RX_clkout), // rx_clkout.export

.tx_parallel_data(TX_parallel_data), // tx_parallel_data.export

.tx_datak(~RX_syncstatus), // tx_datak.export

.rx_parallel_data(RX_parallel_data) // rx_parallel_data.export

//.rx_datak(RX_datak) // rx_datak.export

//output wire [91:0] reconfig_from_xcvr, // reconfig_from_xcvr.reconfig_from_xcvr

//input wire [139:0] reconfig_to_xcvr // reconfig_to_xcvr.reconfig_to_xcvr

);

pll u1(

.refclk(CLK50), // refclk.clk

.rst(RESET), // reset.reset

.outclk_0(CLK65MHz) // outclk0.clk

);

counter u4(

.clock(CLK65MHz),

.cnt_en(RX_syncstatus),

.sclr(RESET),

.q(COUNTCHAR));

constt u5(

.result(CCHAR));

mx u6(

.clock(CLK65MHz),

.data0x(CCHAR),

.data1x(COUNTCHAR),

.sel(RX_syncstatus),

.result(TX_parallel_data));

endmodule