Hello, all,

I have a basic Quartus project that controls the LEDs on the Arrow SoCKit based on the first 4 bits set on the HPS. However, whenever I try to upload the RBF file to the FPGA from the HPS, the kernel encounters an error and then the system locks up:

Unhandled fault: imprecise external abort (0x406) at 0x000bd004

Internal error: : 406 [#2] SMP ARM

Modules linked in: gpio_altera altera_sysid

CPU: 0 PID: 0 Comm: swapper/0 Tainted: G D 3.10.31-ltsi-05172-g28bac3e #1

task: 806db8c0 ti: 806d0000 task.ti: 806d0000

PC is at finish_task_switch+0x78/0xfc

LR is at __schedule+0x250/0x650

pc : [<800524bc>] lr : [<804c5b98>] psr: 60060013

sp : 806d1e98 ip : 806d1eb8 fp : 806d1eb4

r10: bfa8afc0 r9 : bfb7f6c0 r8 : 806cf540

r7 : 00000002 r6 : bf07c780 r5 : 80f5e540 r4 : 00000000

r3 : 00002d93 r2 : 00000000 r1 : 806db8c0 r0 : 80f5e540

Flags: nZCv IRQs on FIQs on Mode SVC_32 ISA ARM Segment kernel

Control: 10c5387d Table: 3f3e404a DAC: 00000015

Process swapper/0 (pid: 0, stack limit = 0x806d0240)

Stack: (0x806d1e98 to 0x806d2000)

1e80: 806cf540 806db8c0

1ea0: bf07c780 806d0038 806d1f64 806d1eb8 804c5b98 80052450 00000000 fee00100

1ec0: 806d83e8 806d843c 806d1eec 806d1ed8 8002c39c 8008a700 8070ae30 806cf540

1ee0: 804c5fd8 806cf540 806d8440 806d8d38 fee0010c 806d8e70 806d1f30 fee00100

1f00: 806d1f2c 806d1f10 80008590 800143c8 8000fa80 60000013 ffffffff 806d1f64

1f20: 806d1f84 8008a588 8000e280 80008534 80f5c7f8 80398af4 806d1f64 806d0000

1f40: 806d0008 806d0000 8070b410 806d83e8 806d843c 00000000 806d1f74 806d1f68

1f60: 804c5fd8 804c5954 806d1f84 806d1f78 804c63c0 804c5fa4 806d1fa4 806d1f88

1f80: 80060b64 804c63b4 8070ae36 804c9ee0 804c63c0 806b3cf0 806d1fb4 806d1fa8

1fa0: 804bd28c 80060a50 806d1ff4 806d1fb8 8067cab4 804bd214 ffffffff ffffffff

1fc0: 8067c5a0 00000000 00000000 806b3cf0 10c5387d 806d83b4 806b3cec 806dc6d4

1fe0: 0000406a 413fc090 00000000 806d1ff8 00008074 8067c80c 00000000 00000000

[<800524bc>] (finish_task_switch+0x78/0xfc) from [<804c5b98>] (__schedule+0x250/0x650)

[<804c5b98>] (__schedule+0x250/0x650) from [<804c5fd8>] (schedule+0x40/0x80)

[<804c5fd8>] (schedule+0x40/0x80) from [<804c63c0>] (schedule_preempt_disabled+0x18/0x1c)

[<804c63c0>] (schedule_preempt_disabled+0x18/0x1c) from [<80060b64>] (cpu_startup_entry+0x120/0x218)

[<80060b64>] (cpu_startup_entry+0x120/0x218) from [<804bd28c>] (rest_init+0x84/0x88)

[<804bd28c>] (rest_init+0x84/0x88) from [<8067cab4>] (start_kernel+0x2b4/0x2c0)

Code: e1c530b0 f57ff04f e320f004 f1080080 (e3540000)

---[ end trace 880a9986d678cc1a ]---

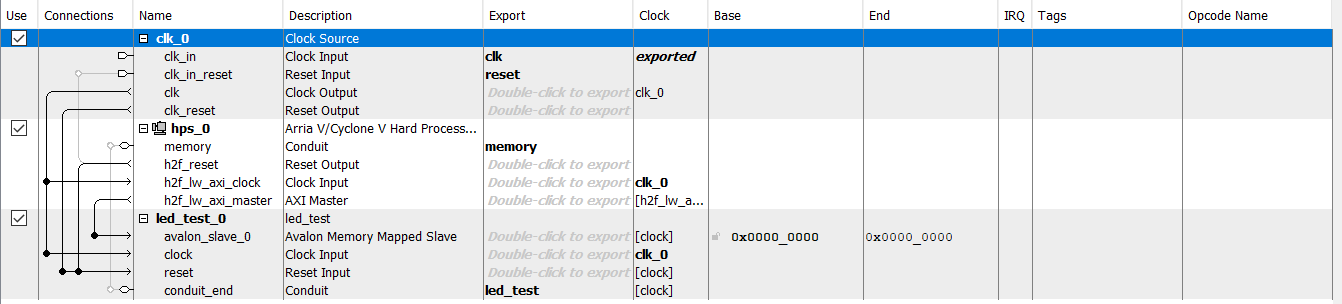

Here is my Qsys diagram:

The main Verilog file:

module Baseline_CV_SoCKit(

//HPS

output [14:0] hps_memory_mem_a,

output [2:0] hps_memory_mem_ba,

output hps_memory_mem_ck,

output hps_memory_mem_ck_n,

output hps_memory_mem_cke,

output hps_memory_mem_cs_n,

output hps_memory_mem_ras_n,

output hps_memory_mem_cas_n,

output hps_memory_mem_we_n,

output hps_memory_mem_reset_n,

inout [39:0] hps_memory_mem_dq,

inout [4:0] hps_memory_mem_dqs,

inout [4:0] hps_memory_mem_dqs_n,

output hps_memory_mem_odt,

output [4:0] hps_memory_mem_dm,

input hps_memory_oct_rzqin,

inout [16:0] HSMC_TX_n,

inout [16:0] HSMC_TX_p,

//clock

input OSC_50_B8A,

//reset

input RESET_n,

//LED

output reg [3:0] LED,

//keys

input [3:0] KEY

);

cyclone_fpga bridge (

.clk_clk(OSC_50_B8A),

.led_test_led(LED),

.memory_mem_a (hps_memory_mem_a),

.memory_mem_ba (hps_memory_mem_ba),

.memory_mem_ck (hps_memory_mem_ck),

.memory_mem_ck_n (hps_memory_mem_ck_n),

.memory_mem_cke (hps_memory_mem_cke),

.memory_mem_cs_n (hps_memory_mem_cs_n),

.memory_mem_ras_n (hps_memory_mem_ras_n),

.memory_mem_cas_n (hps_memory_mem_cas_n),

.memory_mem_we_n (hps_memory_mem_we_n),

.memory_mem_reset_n (hps_memory_mem_reset_n),

.memory_mem_dq (hps_memory_mem_dq),

.memory_mem_dqs (hps_memory_mem_dqs),

.memory_mem_dqs_n (hps_memory_mem_dqs_n),

.memory_mem_odt (hps_memory_mem_odt),

.memory_mem_dm (hps_memory_mem_dm),

.memory_oct_rzqin (hps_memory_oct_rzqin),

.reset_reset_n(KEY[3])

);

endmodule

led_test.v:

module led_test (

input clk,

input reset,

output [3:0] led,

input write,

input [7:0] writedata

);

reg [3:0] led_setting = writedata[3:0];

assign led = led_setting;

endmodule

Could any of you guys please point me in the right direction as to why I can’t upload the code without the SoC freezing?