I was asked this a few times so here are some instructions on how to create a flat FPGA design file and how to set up your SD Card to load it when the Arria 10 SoC Devkit board powers on.

First off is the ‘why flat?’ question. The alternative is Partial Reconfiguration (PR) (which Altera seems pretty excited about), where the FPGA hardware layout will be divided into partitions so each partition can be loaded with a different set of FPGA code (synthesized into gates, etc) along with some higher level control to manage the partitions and the resources they share. The GSRD projects for version 17 and up use this. So the default boot configuration most are starting with will be loading this partial reconfiguration setup.

I can see the utility of this configuration for some applications, but not the ones I am involved in. For my work I want my code to have all the FPGA resources to support my application (so all I/O, all routing resources, etc). So my project is a flat design, where my code is the only thing running in the FPGA (at least nearly). I believe this is how most of us design.

A partial reconfiguration boot setup will place three raw binary files (.rbf) in partition one on the SD Card, along with a uboot program to load them as it boots up the Linux for our HPS processors. (For the GSRD these are (ghrd_10as066n2.rbf, ghrd_10as066n2.core.rbf, and ghrd_10as066n2.periph.rbf.) These separate the I/O definition and the PR management from the logic that goes into the partitions. This allows the partitions to be reloaded at runtime.

A flat configuration has just one .rbf file and a uboot that loads it into the FPGA during startup.

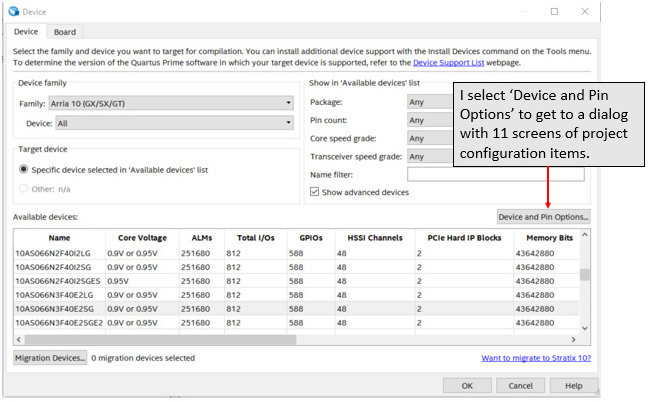

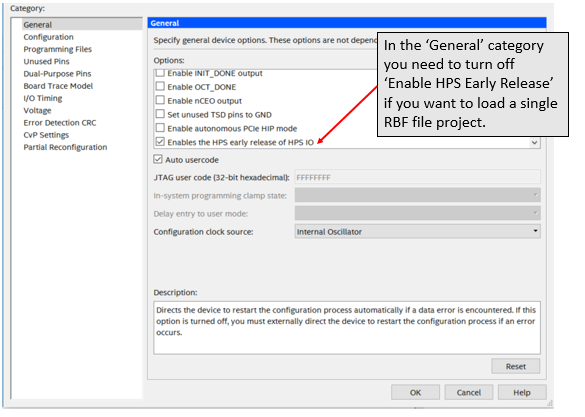

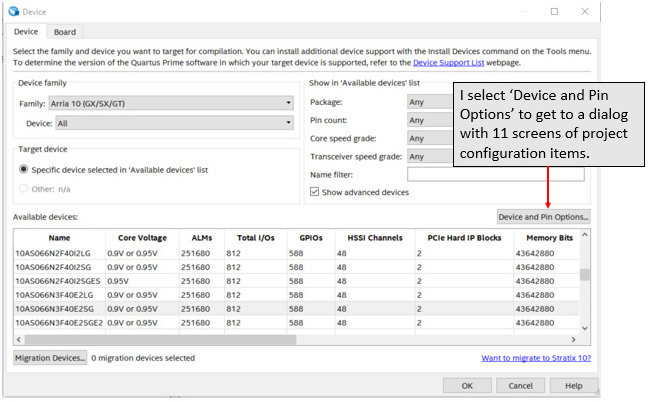

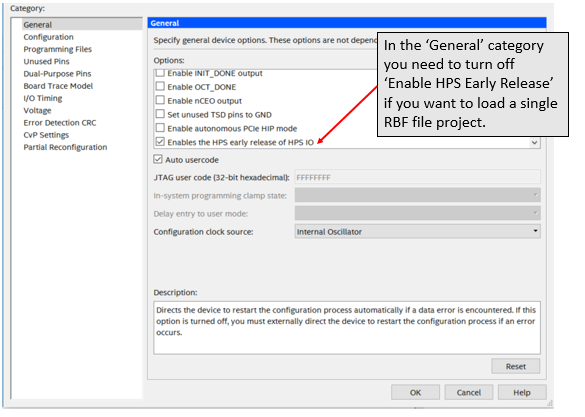

The Quartus setting that determines if your compile is flat or partial reconfiguration is quite obscure. If you look at the dialog from the ‘Device’ item in the ‘Assignments’ menu (I am using Quartus v17.0.2 so this could be different if the Quartus version is different) there is a button titled ‘Device and Pin Options’. When you press this you get a new dialog with 11 categories of project settings. The one setting that changes a project between Partial Reconfiguration and Flat design is in the ‘General’ category and it is at the bottom of the scrolled list, and it is titled ‘Enables the HPS early release of HPS IO’. If this is checked the compile makes a requirement that you use a xxx.periph.rbf and a xxx.core.rbf file. It does not cause the periph and core files to be generated, it only makes them required to boot using uboot. If it is not checked Quartus only creates one .SOF file (which you will later convert to an .RBF file for loading onto your SD Card) and this is all you will need to boot. (If you need to know how to make the other two .rbf files needed for Partial Reconfiguration let me know and I’ll send the tcl commands to do that.)

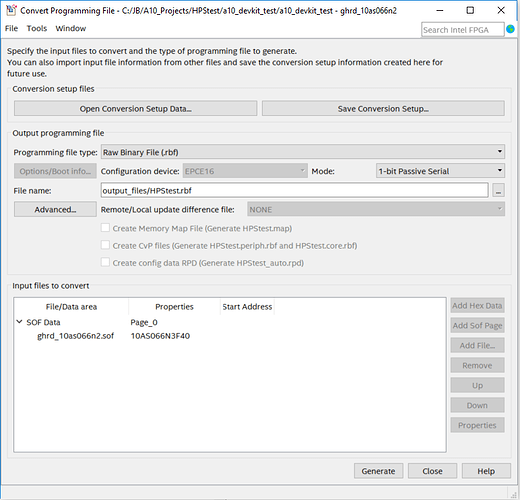

After compiling you convert your flat design .SOF file to an RBF (using the ‘Convert Programming Files’ item under the ‘File’ menu). You can name the RBF file any name you like but it has to have the RBF suffix. Start by chaning the ‘Programming File Type’ to RBF, then select the SOF Data Item down below and click on the ‘Add file’ button. Select your project’s .SOF file in the file dialog and wait for it to load. Now select the file browse button (’…’) next to the output ‘File Name’ above (this will ensure that it places your .RBF file in the output directory along with your other output files). Then click on the ‘Generate’ button at the bottom of the dialog.

The QSYS and Compile generated the handoff files in /hps_isw_handoff subdirectory which will be used to create the uboot loader file. These files are emif.xml and hps.xml. If your QSYS design does not include an emif component for the HPS processor then it will not create the emif.xml file. If you do not have the emif.xml file then the uboot generator will not work. So even if you do not plan to use any on-chip memory from your HPS you must include the emif component.

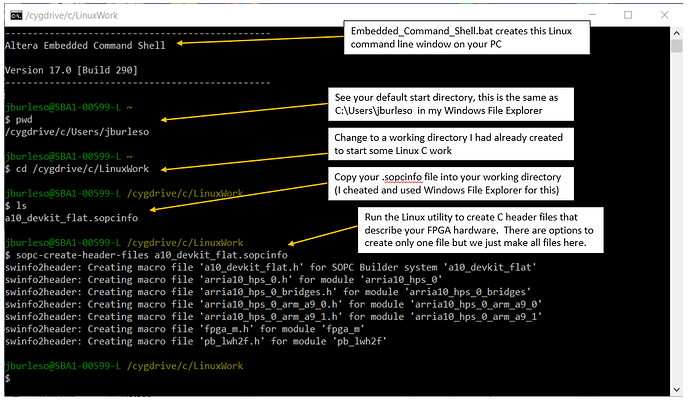

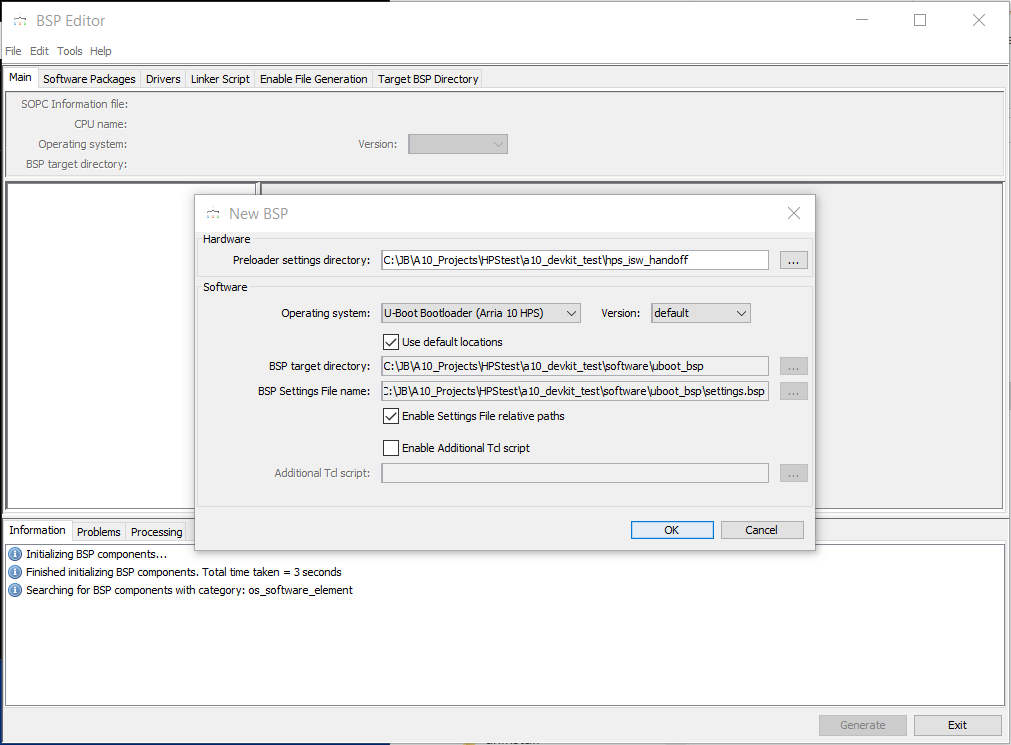

I run the bsp-editor tool from a SOCEDS shell window to create the source files to make a uboot boot file I can use to start my application from the SDCard when the board powers up. To do this in Windows navigate to your Quartus install directory and find the embedded directory (on my machine it is C:\intelFPGA_pro\17.0\embedded ) and execute the program Embedded_Command_Shell.bat. This creates a Linux command window. From the Linux command window run the BSP Editor by entering bsp-editor at the command prompt.

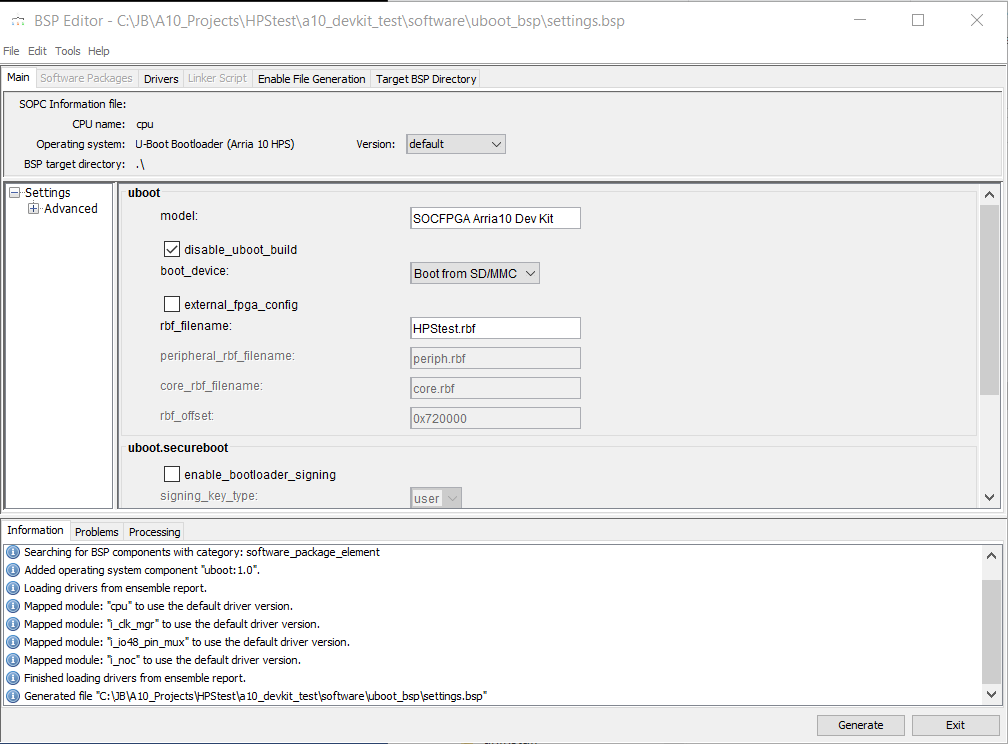

When the window comes up select ‘File’, then ‘New HPS BSP’ and select the ~/hps_isw_handoff directory for your project in the Preloader Settings Directory item. Also use the default locations os the outut files are written to the ~/software directory. When you click OK it will generate some files and present some new entry items. In this window ensure that ‘SOCFPGA Arria 10 Dev Kit’ is selected, and ensure the ‘disable uboot_build_boot_device’ box is checked, then enter your project’s RBF file name. Now click on ‘Generate’ and it will create some C project files. You can now exit the bsp-editor.

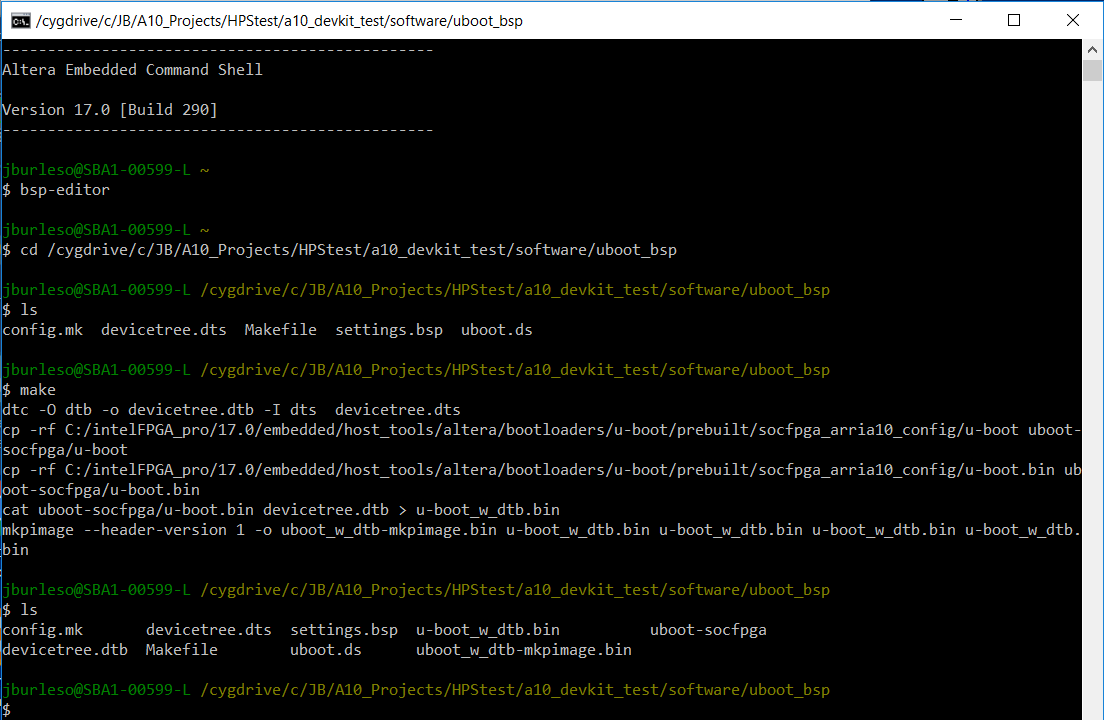

In the SOCEDS Linux window change directory to the uboot source directory specified in the bsp-editor (normally in the /software/uboot_bsp directory ) where you will find some C code files. You can build the project by entering ‘make’ at the Linux prompt.

This will generate two new files uboot_w_dtb_mkpimage.bin and uboot_w_dtb.bin

Copy the uboot_w_dtb-mkpimage.bin to your SD Card. This will be used in partition 3, but if you do this from Windows you will most likely only see partition 1 in the File Manager so you will already be placing files in that place. If you copy the files over to your HPS Linux system (so they could end up in whatever your current working directory is) you can copy the .rbf into partition 1 with the commands below. (Don’t enter the comment portions of the lines below --after the ‘–’ part.)

fdisk -l – this is to discover the SDcard partitions, but we already know where they should be

mkdir /media/sdcard – I usually create a directory for mounting the SD Card in

mount -v /dev/mmcblk0p1 /media/sdcard

cp .rbf /media/sdcard

umount /media/sdcard – dont forget to un-mount the sd card after you are done writing to it

You need a different command to install the uboot binary file into partition 3 (this has to be done in HPS Linux – though I am sure there is a way to do it from Windows but I do not know how) so use the command below to install the uboot into partition 3.

dd if=uboot_w_dtb-mkpimage.bin of=/dev/mmcblk0p3 bs=64k seek=0

Assuming all goes well you are ready to shut down and restart Linux.

shutdown -h now

I generally have about a dozen xxx.rbf files in my partition 1 at any time. Since the uboot is directed to a particular .RBF filename I just rename or copy the RBF files so the one I want to use is in place with the correct name to be booted for the next time the SD Card boots up. This works OK as long as you aren’t adding new devices that you dont have in your current device tree. I need to get around to rebuilding my device tree soon anyway – but that will come later.

It is a very good idea to back up your SD Cards, and a very very good idea when experimenting with new procedures for adding things and removing things from them. That being said I hope you make it safely through the process above and can get started on some straight-forward development using flat design projects.

,

,