@Mikernl

Hi. thank you for your reply. So I have arrow sockit board (cyclone V) board. Transceiver is connected to FPGA. I am running Linux on HPS.

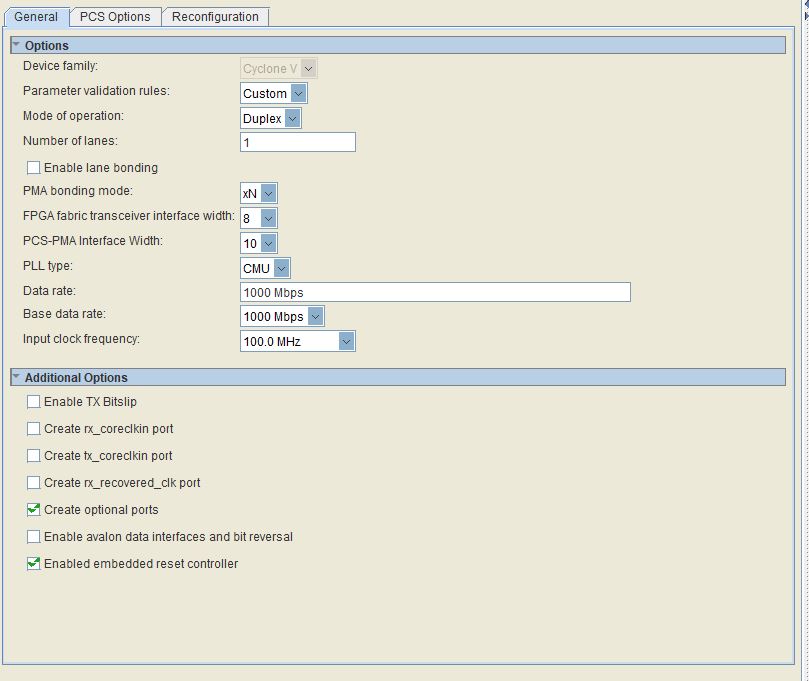

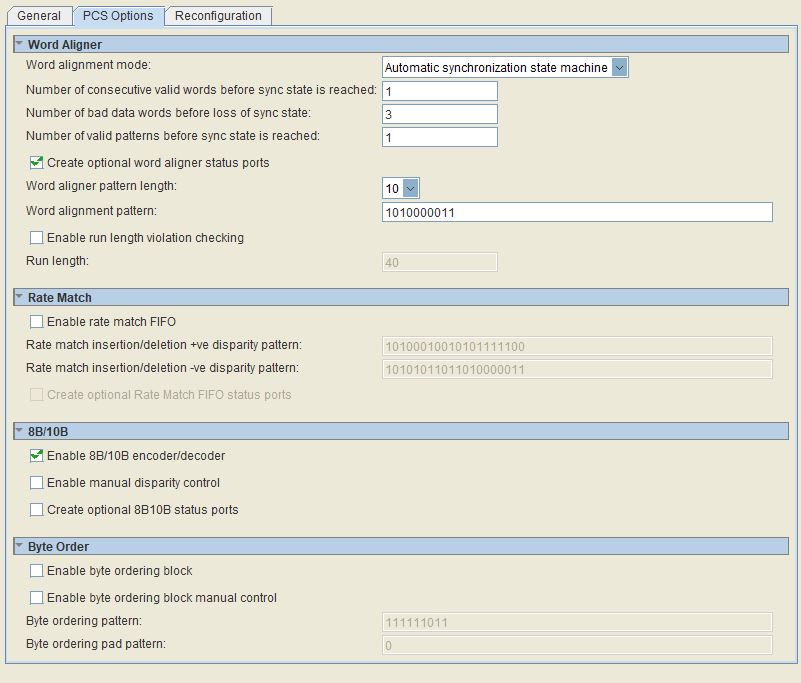

Here are my design details.

-

My HDL design consists of a simple counter (modulus 15; counts from 0 to 14).

-

A constant (8’hBC) which serves as word alligment control character for the transceiver.

-

A mux. Whenever rx_syncstatus output of the transceiver goes high, the mux allows counter output to go to transciever 8 bit tx_parallel data input. Otherwise, constant 8’hBC will go to tx_paralleldata input.

-

A pll generating 100MHz for transceiver tx_clkout generation and transciever pll and internal clocks.

-

Below you can see the transceiver settings.

-

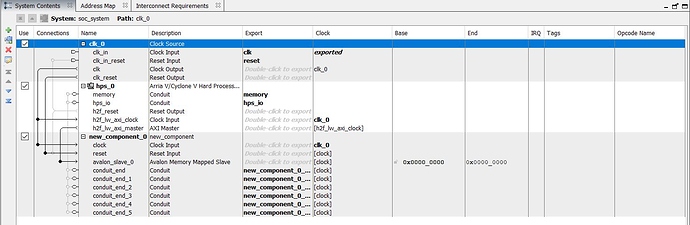

A top level HDL module where I am simply stating that my 8 bit rx_received data goes into a register at every positive edge of tx_clkout. NOW THIS REGISTER VALUE I AM PLANNING TO SEE ON PUTTY TERMINAL: Below is the setup for my qsys where I connect my HPS to this top level register module.

Here is the HDL code for that top level register module that I made:

module xcvrputtysim(

input clk,

input reset,

input read,

output [7:0] readdata,

output tx_serial_data,

input rx_serial_data,

output rx_syncstatus,

output tx_serial_data1,

input rx_serial_data1,

output tx_clkout

);

reg [7:0] Regreaddata;

wire [7:0]rx_parallel_data;

wire outclk;

assign readdata=Regreaddata;

xcvrtop u8(

.clk(clk),

.reset(reset),

.tx_serial_data(tx_serial_data),

.rx_serial_data(rx_serial_data),

.rx_parallel_data(rx_parallel_data),

.rx_syncstatus(rx_syncstatus),

.tx_serial_data1(tx_serial_data1),

.rx_serial_data1(rx_serial_data1),

.tx_clkout(tx_clkout)

);

always @(posedge tx_clkout)

begin

if(reset)

begin

Regreaddata<=0;

end

else if(read)

begin

Regreaddata<=rx_parallel_data;

end

end

endmodule

Can you please help me what can I do? My main system clock (clk) is 50 MHz. I tried but on putty terminal I am seeing strange words like 1129933, 85609, 998812 etc etc. Here is my C code that I tried for HPS:

#include <stdio.h>

#include <unistd.h>

#include <stdlib.h>

#include <stdint.h>

#include <fcntl.h>

#include <sys/mman.h>

#include <sys/types.h>

#include <sys/stat.h>

#include "C:\altera\15.1\embedded\ip\altera\hps\altera_hps\hwlib\include\hwlib.h"

#include "C:\altera\15.1\embedded\ip\altera\hps\altera_hps\hwlib\include\soc_cv_av\socal\socal.h"

#include "C:\altera\15.1\embedded\ip\altera\hps\altera_hps\hwlib\include\soc_cv_av\socal\hps.h"

#include "C:\altera\15.1\embedded\ip\altera\hps\altera_hps\hwlib\include\soc_cv_av\socal\alt_gpio.h"

#include "D:\masterarbeit3\XCVRHWPutty - Copy\hps_0.h"

#define REG_BASE 0xFF200000 /*LWFPGA SLAVE Address*/

#define REG_SPAN 0x00200000

volatile unsigned int *reg_addr; /*this is the pointer that writes to the register. This is our write input*/

void* virtual_base; /*pointer to open device memory file*/

int main ()

{

int fd = EXIT_FAILURE;

fd=open("/dev/mem",(O_RDWR|O_SYNC));

if (fd < 0) {

perror("open");

exit(EXIT_FAILURE);

}

printf("fd is ok\n");

virtual_base=mmap(NULL,REG_SPAN,(PROT_READ|PROT_WRITE),MAP_SHARED,fd,REG_BASE);

printf("virtual base pointer to open device memory file is ok\n");

reg_addr = (unsigned int *) (virtual_base+NEW_COMPONENT_0_BASE); /*accessing base address of register*/

while(1)

{

printf("pointer value is %d\n", *reg_addr);

}

return 0;

}