Hi All,

I want to use the fpga to sdram path in Arria 10 HPS. I want to connect a 256bit AXI interface operating at 125 Mhz from a third party IP to this port. I had a couple of questions:

-

I cannot select a 256 bit data width in HPS parameter editor. The maximum I can go upto is 64bits.

-

If I want to work with 64bit data port but still match the bandwidth (32 Gbps = 256 bits * 125 Mhz) of third party IPs AXI interface, how can I really do it ?

-

How do we decide the frequency of the clock for this fpga-to-sdram port.

-

Which DDR protocol will QSYS configure in the DDR controller. Will it be DDR3 or DDR4. How does Qsys decide this anyway?

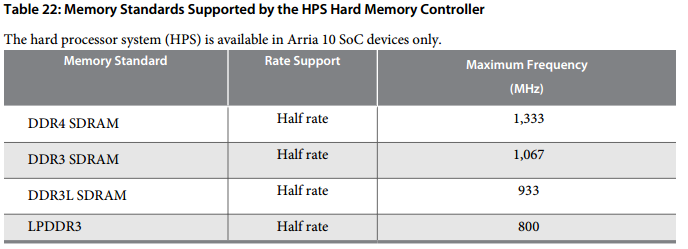

The reason for question 4 is when I went through the Arria 10 overview document, I came to know that it supports following configurations of DDR controller in HPS. Also for Arria 10, when I instantiate the HPS it does not have any option for selecting DDR protocol or DDR memory width like it has for Arria 5.

here is the document link: https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/arria-10/a10_overview.pdf

I want to ensure that I can support maximum bandwidth on this path.

Any suggestions/answers are welcomed !!!