Hi,

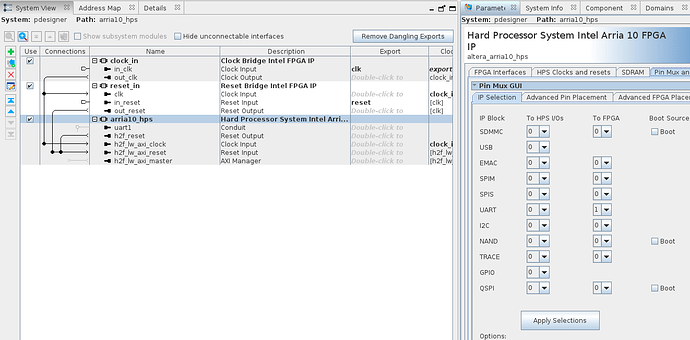

I’m trying to get worked Arria10 SoC Devkit’s FPGA side UART in FPGA side only. It seems that it is connected to HPS’ shared I/O pins. These pins have multiple signals and they must be choosen with a HPS pin mux select. (refer to: https://www.intel.com/content/dam/altera-www/global/en_US/pdfs/literature/dp/arria-10/arria10hps.xls). I search a bit and although not sure the pin mux selection performs in platform designer. So I create a system design with a HPS Arria10 IP. But after that I’m gonna be confused a little bit. When I’m selecting the UART1 from the advence FPGA placement tab, IP creates a UART signal, not just RX/TX a bunch of signals (ready signal, send req, …). But I’m not sure how can I use them. Am I doing rigth thing to use FPGA side UART? In FPGA side UART should just be RX/TX? What should I do now?

Any help will be thankful.