Hiya,

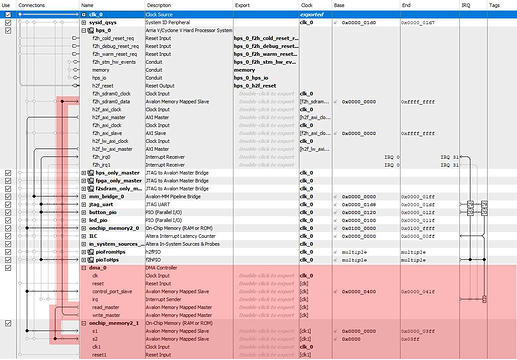

I am using Cyclone 5, and I am developing a bare metal application.

For some testing, I would like to copy data from the onchip-ram to the SDRAM using the the IP DMAC.

I would like to move 80 bytes from the OCRAM to SDRAM with base address 0x02000000.

My code can be compiled , and runs (in debugg mode on the processor). The relevant code sections are:

/SDRAM-FPGA-BRIDGE/

#define SDRAMC_BASE 0xFFC25080 /0xFFC2_0000 +0x5080/

uint32_t volatile * const sdramc_status_ptr = (uint32_t *) SDRAMC_BASE;/DMAC Settings/

#define DMA_STATUS_BASE 0xC0000400 /0xC000_0000 + 0x0400/

uint32_t volatile * const dma_status_ptr = (uint32_t *) DMA_STATUS_BASE;/OCRAM/

#define OCRAM_BASE 0xC0000000

uint32_t volatile * const ocram_base_ptr = (uint32_t *) OCRAM_BASE;int main(void)

{

/…/

/Enable SDRAM-FPGA Bridge/

*(sdramc_status_ptr)=0x3FFF;/DMA-Source/

void* fpga_ocr_dmac=0;/DMA Settings:/

(dma_status_ptr)=0x0;

(dma_status_ptr +1) = (uint32_t) fpga_ocr_dmac; / Base Address Read-Master/

(dma_status_ptr +2) = 0x02000000; / Base Address Write-Master*/

(dma_status_ptr +3) = 80; / Transferlengh in bytes (20 words)/

(dma_status_ptr +6) = 0x284; / Set WCON,RCON, LEEN and Word 0b0010_1000_0100//wait a moment/

int index;

for(index=0;index <1000;++index{__asm{nop};}/DMA go/

*(dma_status_ptr +6) = (dma_status_ptr +6) |(0x8); / Set the go bit/THIS WHILE LOOP IS NEVER LEFT/

while(( ((dma_status_ptr) & 0x001) ==0) ){} / spinn until ‘transfer-done-bit’ is 1 /

printf(“DMA Transfer Done \n”);

printf(“SDRAM %d”,( (int32_t *) (0x02000000)) );

}

The while loop is never left, I am left to believe that the transmission was never executed at all. I suppose there is mystake in the qsys implementation.

I would be gratefull for any hints, for possible mystakes. Or if somebody could point out some other fundamental errors.

Many thanks in Advance

Thomas