Greeting everyone! I am relatively new to this forum (but not rocketboard wiki), and if this is common question, feel free to send me a link that answers my question, thank you

For reference, I am running 4.14.30 Linux kernel.

I am currently working with Cyclone V socfpga using IoTOctopus board. I am attempting to configure a basic device tree to communicate with a soft IP UART module on FPGA fabric. There are two resources that are useful that I’ve found: How to create a device tree (Rocketboard) and the official kernel docs about FPGA interface peripherals here.

For record, I’ve attempted to implement a device tree overlay based on RocketBoard page, but I’ve had trouble as up on applying the probe fails with error -22, which is either maxed out number of ports or incorrect memory location (later seems likely). I am trying to remedy my confusion to solve this problem.

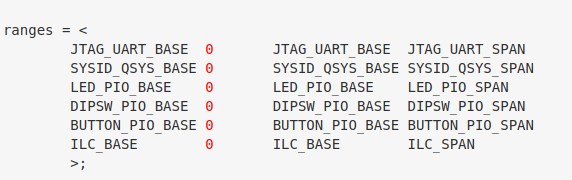

Q1. What is the exact meaning of ‘ranges’ in in relation to child nodes?

I understand that ranges can be used to remap from one address region to another. In that case how come each entry of begin with the absolute address of the peripheral and not the bridge itself? I figured that it may be that the bus address is set using chip select of 0, but then where are the address ranges for buses themselves are configured?

Q2. Does anyone have experience using partial reconfigure device tree options?

The kernel docs indicate that it is possible to use device tree overlays to allow automatic reprogramming of the FPGA fabric, either partially or fully. Does anyone have advice on how to implement that (or at least helpful links)? There is info about it in kernel docs, but once again I am uncertain about the validity of those solutions.

Q3. Why are the configurations from Rocketboard and the kernel docs different?

In kernel docs, the fpga region is a child node to fpga bridge, which makes sense to me, given that a peripheral is tied to specific bus. However socfpga.dtsi defines fpga bridge and base region parallel to each other (which I assume is the correct way). Does anyone know what is the difference ?

Thank you so much!