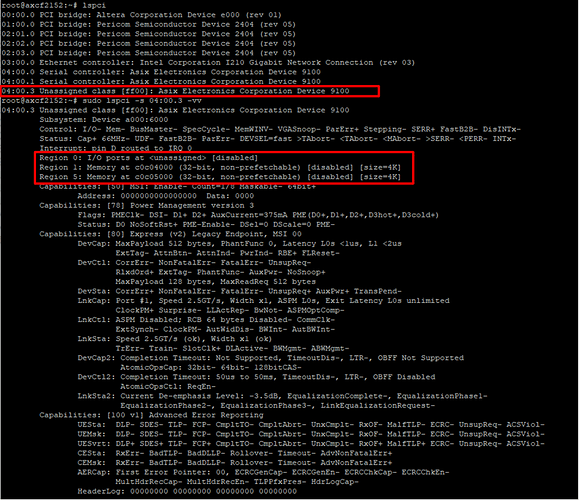

The AX99100 device chip is connected to the Cyclone V 5CSXFC4C6 via PCIe. However, the I/O space of the device chip does not seem to be accessible from the Cyclone V (figure below). The I/O space is declared as “unassigned”.

The operating system running on the HPS is Linux with kernel version 4.14.

The FPGA image is loaded from the operating system during the boot process. In the FPGA, the “Avalon-MM Cyclone V Hard IP for PCI Express” IP core is instantiated as root port, to which the device chip is also connected.

Is it due to the FPGA, the IP core or the Linux root driver?