Hello

I’m new to Cyclone V tools and am struggling to get the stock GHRD to compiile as described in the manual. Would some kind and experienced soul take a quick peek to find out what I’m doing wrong?

It’s a DE10-Nano Cylcone V development board rev B2 from Terasic, and I’m following the instructions in the User Manual (rev B2) chapter 7 “Examples for using both the HPS SoC and FPGA”

It’s on a freshly-installed Ubuntu 16.04.3 server, at AWS.

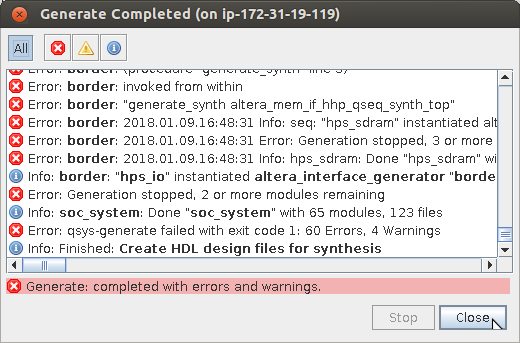

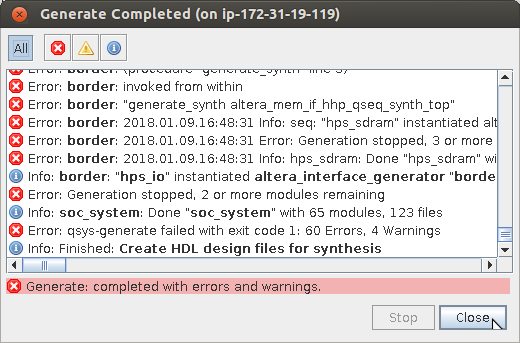

It’s a straightforward compilation of the GHRD (open project .qpf file, Tools>Qsys: open .qsys file, Generate>Generate HDL). Following the instructions very carefully, I get four warnings and screenfuls of errors, the first of which is something to do with a missing file hps_AC_ROM.hex

Error: border: Error during execution of script generate_hps_sdram.tcl: seq: \

add_fileset_file: \

No such file /tmp/alt7540_4530398708016069914.dir/0003_seq_gen/hps_AC_ROM.hex

Error: border: Error during execution of script generate_hps_sdram.tcl: \

Generation stopped, 3 or more modules remaining

Error: border: Execution of script generate_hps_sdram.tcl failed

The warnings were

Warning: hps_0.f2h_irq0: Cannot connect clock for irq_mapper_001.sender

Warning: hps_0.f2h_irq0: Cannot connect reset for irq_mapper_001.sender

Warning: hps_0.f2h_irq1: Cannot connect clock for irq_mapper_002.sender

Warning: hps_0.f2h_irq1: Cannot connect reset for irq_mapper_002.sender

Can some kind soul tell me what I should do to get it compiled? (Complete details of my steps below).

Many thanks,

Jonathan.

Below here is just exact details of what I was doing, probably no need to read

Compilation system is freshly installed Ubuntu 16.04 LTS server

CDROM image was from Terasic: DE10-Nano_v.1.2.4_HWrevB2_SystemCD.zip

This is my project directory:

cp -Rp cdrom/Demonstrations/SoC_FPGA/DE10_NANO_SoC_GHRD ~/GHRD

File DE10_NANO_SoC_GHRD.qsf seems to say it’s done in Quartus 16.0

set_global_assignment -name TOP_LEVEL_ENTITY "DE10_NANO_SoC_GHRD"

set_global_assignment -name LAST_QUARTUS_VERSION 16.0.2

set_global_assignment -name PROJECT_CREATION_TIME_DATE "17:14:54 MARCH 04,2015"

Because the manual says “16.0 or greater”, and this file was done with 16.0, that’s what I’m using. (I actually tried with 17.1, same problems.)

cadbox$ quartus

- File > Open Project: choose

DE10_NANO_SoC_GHRD.qpf - Tools > Qsys

- (Qsys wants file) Choose

soc_system.qsys - Validates okay, 7 green messages

- I see connection map

- Click on Address Map Tab

- Click on arrow to sort by addresses

- Looks same as in manual except the addresses for

hps_0.f2h_sdram0_datawhich don’t appear in manual.

- (Qsys) Generate > Generate HDL …

- Defaults for this form:

- Lots of errors

Just for completeness, this is how I got the tools installed in case I’ve done something wrong here.

wget http://download.altera.com/akdlm/software/acdsinst/16.0/211/ib_tar/Quartus-lite-16.0.0.211-linux.tar

tar xvf Quartus-lite-16.0.0.211-linux.tar

cd components/

./QuartusLiteSetup-16.0.0.211-linux.run --mode unattended --unattendedmodeui none --installdir /mnt/altera/16.0

wget http://download.altera.com/akdlm/software/acdsinst/16.0/211/ib_installers/SoCEDSSetup-16.0.0.211-linux.run

chmod 775 SoCEDSSetup-16.0.0.211-linux.run

./SoCEDSSetup-16.0.0.211-linux.run --mode unattended --unattendedmodeui none --installdir /mnt/altera/16.0

# Fix PATH in .bashrc, log out, log in, Check environment has QSYS_ROOTDIR and suitable path:

cadbox$ echo $QSYS_ROOTDIR

/mnt/altera/16.0/quartus/sopc_builder/bin

cadbox$ which quartus

/mnt/altera/16.0/quartus/bin/quartus

cadbox$ quartus_sh --version

Quartus Prime Shell

Version 16.0.0 Build 211 04/27/2016 SJ Lite Edition