It has nothing to do with software.

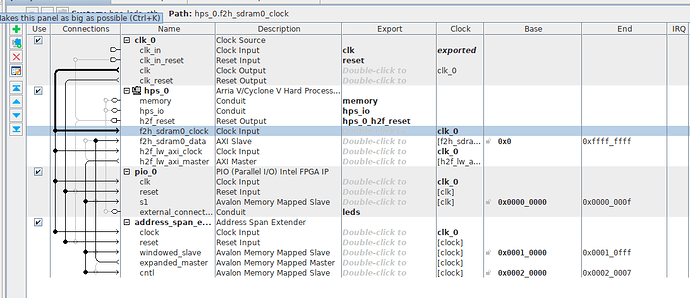

I created a design with an address space extender IP with a 64K window that would allow me to write to different 64K areas of the SDRAM via a register that would set base address for a given 64K area. I tried doing a simple write via HPS_AXI_LW (which I proved worked in Signal Tap), through this IP and to the SDRAM interface. I did this in u-boot console and when I initiated the transaction, u-boot froze and then rebooted. This is definitely a HW/FW problem. For reference, I had GPIO at address 0x0 in the FPGA LW BASE address space.

=> mw FF200000 000000ff

=> mw FF220000 00000000

=> mw FF220004 40000000

=> md FF200000 1

ff200000: 000000ff …

=> md FF210000 1

ff210000:

I am reading about SDRAM clocking. I think some of the blocks are supposed to be set up by u-boot via settings pll_config.h, which is created by running qts_filter.sh on you Quartus project. I think your device has the same flow that includes qts_filter. Do you mind sending me your pll_config.h file when you get a chance?