As the title says, I’ve enabled the FPGA2SDRAM interface in my HPS and have written an Avalon Memory Mapped Host/Master to write to a specific memory location.

It’s a very simple code, based off the template in platform designer and it works fine:

`timescale 1 ps / 1 ps

module mem_write (

output logic [31:0] avm_m0_address, // avm_m0.address

input logic avm_m0_waitrequest, // .waitrequest

output logic avm_m0_write, // .write

output logic [31:0] avm_m0_writedata, // .writedata

input logic clk, // clock.clk

input logic reset, // reset.reset

input logic [31:0] in_address

);

reg [31:0] cnt;

assign avm_m0_address = in_address;

assign avm_m0_write = 1'b1;

assign avm_m0_writedata = {30'd0, cnt[26], cnt[25]};

always_ff @(posedge clk) begin

cnt <= cnt + 1'b1;

end

endmodule

I hardcoded in_address in my top level design to be 32'h20000000 (512MB).

This works fine and I can see it cycling through 0-3 at 0x20000000 at regular intervals with the command:

busybox devmem 0x20000000

But when I try to do the reverse, i.e. read from the same memory location, linux hangs.

Here is my code:

`timescale 1 ps / 1 ps

module mem_read (

output logic [31:0] avm_m0_address, // avm_m0.address

output logic avm_m0_read, // .read

input logic avm_m0_waitrequest, // .waitrequest

input logic [31:0] avm_m0_readdata, // .readdata

input logic clk, // clock.clk

input logic reset, // reset.reset

input logic [31:0] in_address,

output logic [31:0] out_data

);

reg [31:0] readdata;

assign avm_m0_address = in_address;

assign out_data = readdata;

assign avm_m0_read = 1'b1;

always_ff @(posedge clk) begin

if (reset) begin

readdata <= 32'd0;

end else begin

if (avm_m0_waitrequest) begin

readdata <= readdata;

end else begin

readdata <= avm_m0_readdata;

end

end

end

endmodule

Is there something wrong with my code?

I’ve set up the FPGA2SDRAM in HPS to be bi-directional and 256 bits.

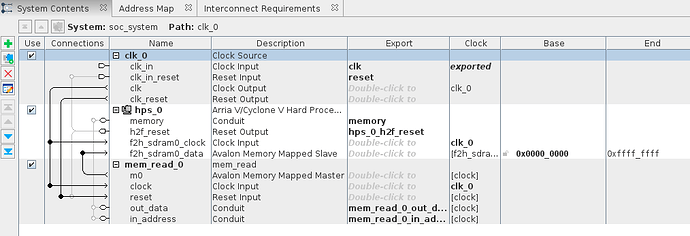

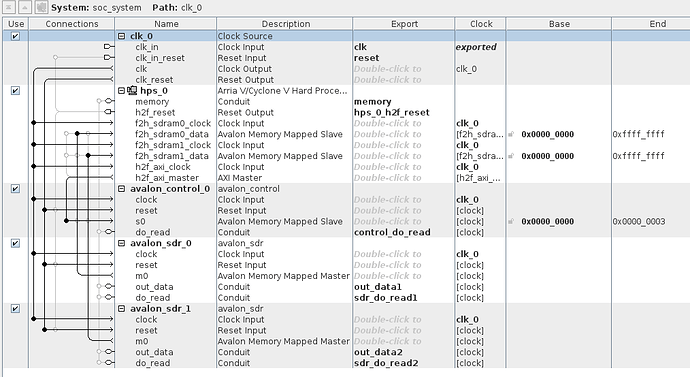

Here is a screenshot of platform designer: