Hi everybody,

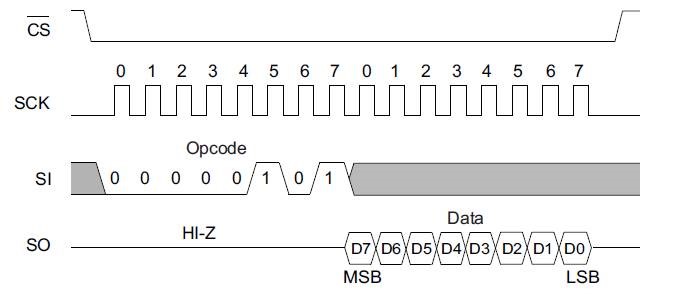

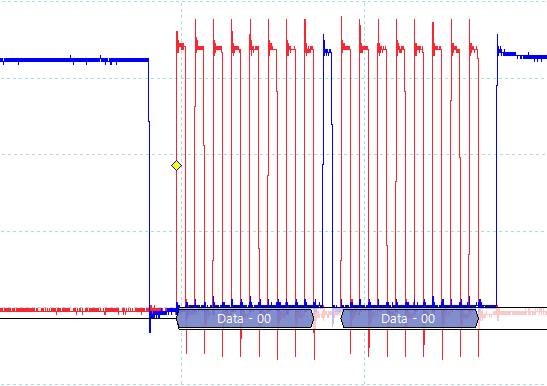

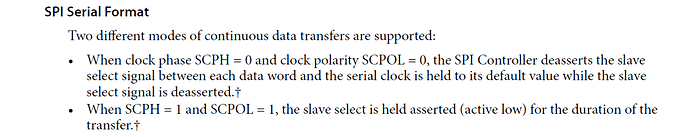

I wired an SPI EEPROM/NVRAM to the DE10nano board (using the LTC header). I implemented a bare metal application that should read the Status Register of the NVRAM (using opcode 0x05). Unfortunately the nCS goes HIGH and the CLK is disabled after the opcode was transmitted so the NVRAM will never answer to the opcode because it is disabled.

The following picture shows the signals that should be created:

I already checked my implementation according to the “Cyclone V Hard Processor System

Technical Reference Manual” but I did not realized a mistake in my implementation.

Does someone of you has a similar issue or a bugfix?

Kind regards

Dan