I have a Stratix 10 Soc Development kit and it is booting with HPS first with the root file system on the SD card. The Core rbf is being loaded with uboot using fatload… fpga load… and then boot. I can interact with the memory mapped space with the hardware at expected addresses from the HPS, so I think the core rbf loaded correctly. When trying to use signal tap, I can see the FPGA in the JTAG chain but it always tells me Program the device to continue. I know this is the stp file that corresponds with this compile, so I am not sure what is wrong. Typically when I have seen this on other boards, its because I have chosen the wrong stp file or somehow corrupted it.

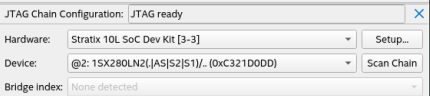

Here is my selected jtag device.

There are two devices in the device list and I have tried both of them.

This design is based on the 2020.05 GSRD and the was built with the instructions in Stratix 10 SoC GSRD with the HPS first linux patch from Stratix 10 SoC HPS First Single QSPI Flash Boot

Quartus version: 20.1

Any Ideas are appreciated. Thanks!