Hello,

I’ve been working to bring up the Stratix10soc IEEE 1588 example found here:

The boards available to me did not include the L tile versions (i have 2 H tile and 2 L tile ES boards) so I had to rebuild the HDL which seemed to work fine. I also used Quartus pro 21.4 for this. I rebuilt using the project archive following the instructions. I did run into some some issues with booting but I found a way to work around that.

Found U-Boot script /boot.scr.uimg

2195 bytes read in 4 ms (535.2 KiB/s)

## Executing script at 05ff0000

crc32+ Trying to boot Linux from device mmc0

Found kernel in mmc0

12687859 bytes read in 616 ms (19.6 MiB/s)

## Loading kernel from FIT Image at 02000000 ...

Could not find configuration node

ERROR: can't get kernel image!

SCRIPT FAILED: continuing...

** Unable to read file / **

Failed to load '/'

libfdt fdt_check_header(): FDT_ERR_BADMAGIC

Scanning disk dwmmc0@ff808000.blk...

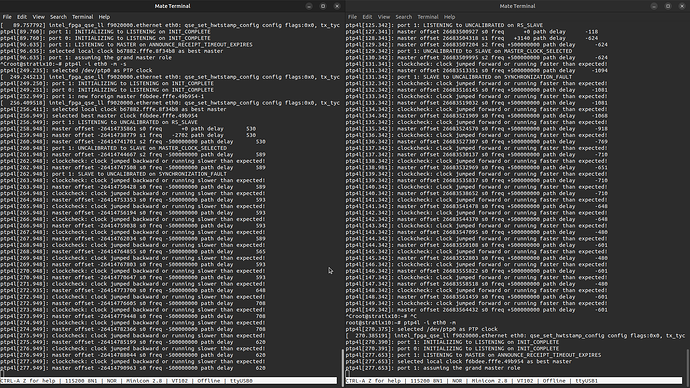

In the end it seems like the two boards have achieved a link, it tested at about 1.3gbps but the PTP synchronization is not working. I tried switching their roles and in one case the slave complains the clock is faster and if the other board is the slave it says the clock is slower then expected.

I checked if the Clock Controller application is working. I used a scope to look at the SI5341 Out2 and and saw 125.0 MHz for both boards although it looks like it does not matter whether I set the clock or not, the behavior looks the same. Does anybody know what might be causing this issue?

Thanks,

Sergiu