Hi all, I am going to make a project on a cyclone V Sockit board. The project works as following:

- HPS (ARM processor) extracts data from a memory and puts it in a FIFO.

- When this FIFO is full, it transfers the data over a transceiver to another cyclone V Sockit board.

- That transceiver on second Sockit board puts the received data into a FIFO and then from that fifo the HPS takes the data and puts it into the memory.

- The transfer of data from one fifo over the transceiver to another fifo should only be happen if there is enough space into the fifo.

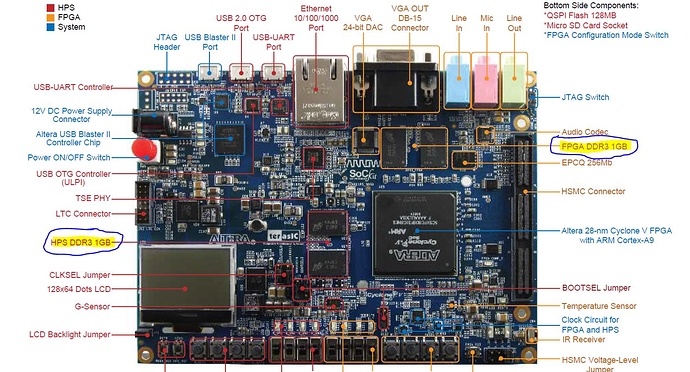

Now, I need your advice about this memory from which HPS extracts the data. there is 1GB of DDR3 SDRAM on sockit board for each of HPS and FPGA. Can I use this memory for this purpose? Which ip core do I need to utilise this memory? And any resources or tutorial for this memory?

Here you can see these memories